Osciloskop na PC.

Po dlouhé době se opět dostávám k projektu osciloskopu na PC. Konstrukcí tohoto typu je na Webu i v časopisech spousta, ale to, co jsem zatím zkoumal mělo vždy nějaké ale...

Tak jsem se pustil do vlastní konstrukce. Původně to měl být jednoduchý vzorkovací osciloskop s levnými pomalými převodníky A/D. Vtip spočívá v tom, že se musí generovat pila, stejně jako u analogu a ta se náhodně vzorkuje spolu se vstupním signálem. Z toho lze zrekonstruovat velmi jednoduše průběh vstupního signálu – zobrazovat body s „x“-ovou souřadnicí, danou vzorkem pily, souřadnice „y“ je dána vzorkem vstupního signálu. Je tedy možné pozorovat jen periodické průběhy, ale je možné dosáhnout velké šířky pásma, protože ta závisí jen na kvalitě vzorkovacího obvodu. Toto řešení se ukázalo být v praxi nepoužitelné – bodové zobrazení a podmínka periodičnosti jsou zde příliš svazující – signály typu „obdélník“ se pozorují opravdu velmi špatně, i když body zhasínají postupně jako u analogu (dosvit).

Konstrukce z Webu jsou buď jednoduché, ale pomalé nebo příliš složité. Docela schopná byla konstrukce s hardwarovým FIFO IDT2102, ale připojení na paralelní port a analogový trigger, to prostě chtělo předělat. A tak se nabalovala logika, dál už to nešlo a tak jsem se začal učit VHDL. Nyní je koncepce zhruba takováto:

8-bit A/D -> FPGA Xilinx -> FT245 -> USB -> PC

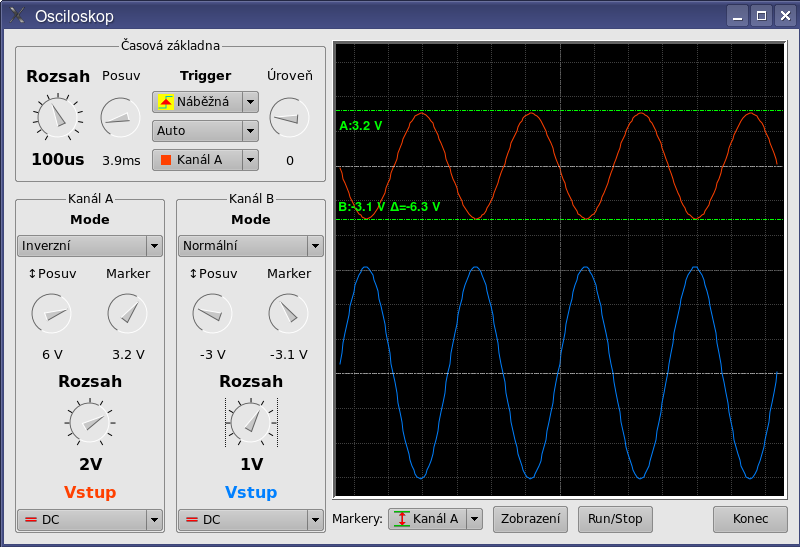

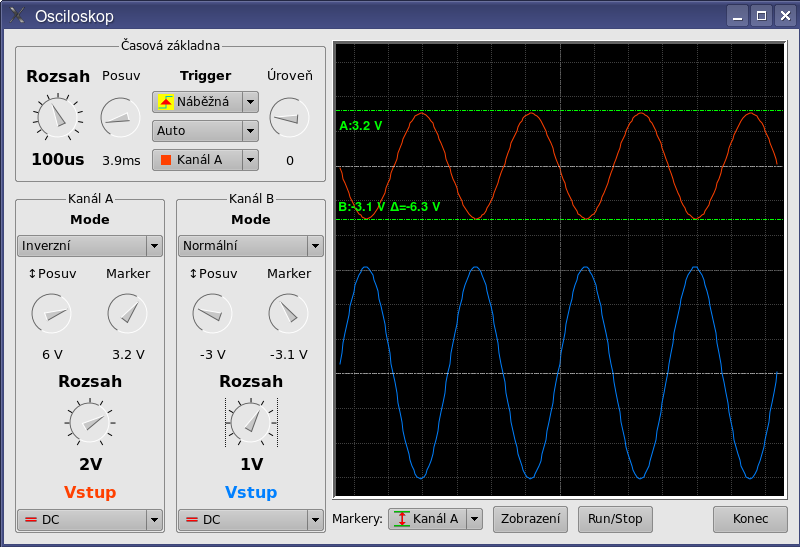

Do PC se nebude přenášet celý datový tok – pro FT245 je to max. 1 MB/s a to je málo – FPGA může řešit mimo FIFO i podmínku triggeru. Takto bude možné použít 2 kanály se vzorkováním 40 MS/s. Ovládací program by měl fungovat pod Windows i pod Linuxem – tvořím ho v Qt4. Xicht by měl vypadat asi takto :

Zbývá dodělat :

Vybrat A/D převodníky – něco jako AD9283.

Navrhnout a odladit vstupní zesilovač a děliče.

Odladit ve VHDL trigger.

Dopsat ovládací program a celé to skloubit dohromady.

Zima 2008

Předělána koncepce.

Rozhodl jsem se použít v konstrukci 32 bitový mikroprocesor ARM od Atmelu. Na první pohled se to zdá být zbytečné, ale procesor má USB a tak se nabízí použít jej místo FT245. Výhodou tohoto uspořádání je, že je možné rozšířit komunikační protokol a data pro inicializaci FPGA posílat přímo z počítače a ne z konfigurační paměti. Tím ušetřím tuto poměrně drahou součástku a získám tak možnost velké flexibility FPGA firmware. Zjednoduší se i vlastní komunikace mezi FPGA a řídícím počítačem, resp. ta její část, kterou zpracovává FPGA. A naučit se programovat ARM7TDMI také není k zahození.